## A Review on Crosstalk in On-Chip High Speed VLSI Interconnects

Hitlendra Pratap Singh<sup>1</sup>, Dr. G.S. Virdi<sup>2</sup> <sup>1</sup>Dept. of ECE, MIET, Meerut, India-250005 <sup>2</sup>GGSCMT Mohali, India-140301

**Abstract-** As process technologies scale into deep submicrometer wiring in this environment introduces resistive, capacitive, and inductive parasitics. When the operating clock frequency is used beyond GHz in on-chip environment then Crosstalk, crosstalk delay, speed, energy consumption, signal integrity, and reliability affects due to these parasitics. On-chip signal crosstalk is a function of switching activity pattern, coupling parasitics, and signal timing.

Indext Terms- Wires Parasitic, Bus, Crosstalk, Crosstalk delay, CACs, Interconnect.

#### 1. Introduction

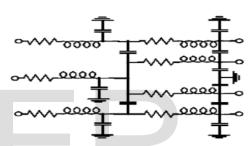

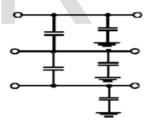

In DSM and UDSM technology environment due to scaling of devices and speed of circuit is increasing because of yearly change in technology, the parasitic effect introduces in Onchip interconnect wires which dominate relevant metrics of digital integrated circuits such as speed, energy consumption, delay, crosstalk, and signal integrity. The average length of interconnect wire is increasing yearly in comparison to device dimension. Therefore, careful investigation of crosstalk, dealy, and power consumption is required in On-Chip VLSI interconnect. To investigate these parameters interconnect can be modeled as capacitive, resistive, and inductive parasitic. Interconnect parasitics like capacitance, resistance, and inductance are not included in a single physical point but are distributed over the entire length of the wire. A fully fledged circuit model that illustrate all the parasitic capacitance, resistance, and inductance of the interconnections is shown in below figure (1) and a circuit model with capacitive only parasitic shown in figure (2).

Figure (1) Wire model with full-fledged parasitic [25]

Figure (2) Wire model with capacitive parasitic [25]

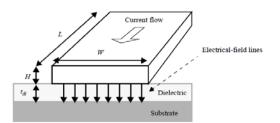

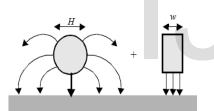

consider first a simple rectangular wire placed above the semiconductor substrate, as shown in Figure (3). If the width of the wire is substantially larger than the thickness of the insulating material, it may be assumed that the electrical-field lines are orthogonal to the capacitor plates, and that the parallel-plate capacitor model can model its capacitance also called area capacitance.

Figure (3) Parallel plate capacitance model of Interconnect wire [25]

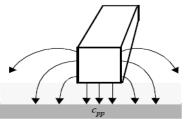

The model shown in figure (4) decomposes the capacitance into two contributions: a parallel plate capacitance, and a fringing capacitance, modeled by a cylindrical wire with a diameter equal to the thickness of the wire

Figure (4) Fringing fields [25]

Figure (5) Model of fringing field capacitance [25]

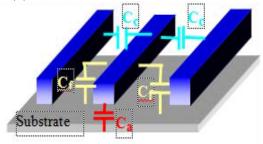

As per the International technology roadmap for semiconductors (ITRS), the packing density is increasing year by year and technology scale down to beyond nanometer scale and will contain more than billion transistors and operate well beyond clock speed 10GHz. Therefore, transmition of power signal, ground signal, clock, data, address, and other control signals through interconnects in such a high speed, high complexity environment the signals from one lines to another lines affect each other because in this environment interconnect behaves as а transmission line and modeled as RLC or RC type circuit network. Due to crosstalk delay, signal integrity, and power consumption deficiencies will arise. The components, which affect the behavior of the on-chip bus these are mainly internal parasitic capacitances of the transistor, interconnect capacitances, and input capacitances of the fan out gates. To simplify the parasitic capacitance model of interconnect it contains mainly three capacitances  $C_a$  area capacitance to substrate ,  $C_f$  fringe or side-wall capacitance to substrate , and  $C_c$  cross-coupling capacitance between two adjacent shapes which shown in figure (5).

Figure (5) parasitic capacitance model

#### 2. Crosstalk

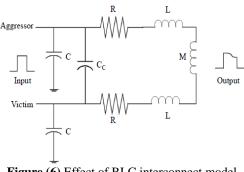

Crosstalk is an unwanted coupling from a neighboring signal wire to a network node introduces an interference that is generally called crosstalk and the resulting disturbance acts as a noise. This can be of both inductive and capacitive type coupling. This is illustrated in figure (6). The coupling between the groups of the three wires is classified into five Types depending upon the nature of transitions of signals in the wire that are Type-0, Type-1, Type-2, Type-3 and Type-4. This is illustrated in Table (1). Where  $\gamma = C_c/C_1$  (i.e. ratio of coupling capacitance to load capacitance).

Figure (6) Effect of RLC interconnect model

| Crosstalk | Transition Patterns                                                                                                                                                                                                                                                                       | Crosstalk |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Class     | $(\mathbf{d}_{k-1}, \mathbf{d}_{k}, \mathbf{d}_{k+1})$                                                                                                                                                                                                                                    |           |

| 1         | $ \begin{array}{c} \uparrow -\uparrow, \downarrow -\downarrow, \uparrow -\downarrow, \downarrow -\uparrow, \uparrow -\\ -,\downarrow,,\uparrow, \downarrow -\\ - \end{array} $                                                                                                            | 0         |

| 2         | <b>,</b> ↑↑↑, ↓↓↓                                                                                                                                                                                                                                                                         | 1         |

| 3         | $\begin{vmatrix} - & \uparrow, \uparrow , \downarrow, \downarrow , \\ \uparrow \uparrow - , \downarrow \downarrow - , - \uparrow \uparrow, - \downarrow \downarrow \end{vmatrix}$                                                                                                         | 1+γ       |

| 4         | $ \begin{array}{c} -\uparrow -, \uparrow - \uparrow, \uparrow - \downarrow, -\downarrow -, \\ \downarrow - \downarrow, \downarrow -\uparrow,  \downarrow \downarrow \uparrow, \uparrow \uparrow \downarrow, \\ \downarrow \uparrow \uparrow, \uparrow \downarrow \downarrow \end{array} $ | 1+2γ      |

| 5         | $-\downarrow\uparrow, -\uparrow\downarrow, \uparrow\downarrow-, \downarrow\uparrow-$                                                                                                                                                                                                      | 1+3γ      |

| 6         | $\downarrow\uparrow\downarrow,\uparrow\downarrow\uparrow$                                                                                                                                                                                                                                 | 1+4γ      |

Table (1) Crosstalk Classes and Corresponding Delays:

\*The symbols  $\uparrow$ ,  $\downarrow$ , – are used to indicate  $0 \rightarrow 1$ ,  $1 \rightarrow 0$  and  $1 \rightarrow 1$  (or)  $0 \rightarrow 0$  transitions

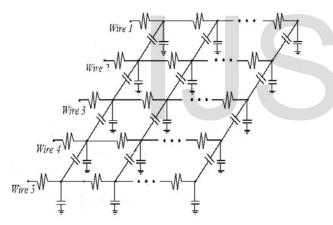

Figure (7) Distributed RC model for five wires [5]

Crosstalk problems arise due to on-chip crosstalk between neighboring wires, which becomes more pronounced at deep submicron regime. Crosstalk occurs when a signal on a wire (aggressor) affects the signal on a neighboring wire (victim) due to capacitive and inductive coupling between neighboring wires. Crosstalk may cause violation of timing constraints by hastening or delaying the signal transition or logic failure by inducing a glitch or spurious signal transition on the victim wire crosstalk is a function of coupling

**TABLE (2)** SUBCLASSIFICATION OF PATTERNS BY

SIGNAL EXPRESSIONSON WIRE 3 IN A FIVE-WIRE

DUB [5]

| BUS [5] |                                                  |            |                                                                                                       |

|---------|--------------------------------------------------|------------|-------------------------------------------------------------------------------------------------------|

| Subclas | Patter                                           | Subcla     |                                                                                                       |

| s k     | ns                                               | ss k       | Patterns                                                                                              |

| ~       |                                                  | ~~         |                                                                                                       |

|         |                                                  |            |                                                                                                       |

|         |                                                  |            |                                                                                                       |

| 1       | ****                                             |            | ↑, ↑-↑-↓, ↓-                                                                                          |

| 1       | $\uparrow \uparrow \uparrow \uparrow \uparrow$   | 10         | ↑-↑                                                                                                   |

|         | - 1 1 1 1,                                       | 13         | $\uparrow\uparrow\downarrow\downarrow$ , $\uparrow\uparrow\downarrow\downarrow\downarrow$ ,           |

| 2       | <u> </u>                                         |            | ↓↑↑↓↑                                                                                                 |

|         | <b>↑-</b> ↑↑↑,                                   |            | -↓↑↑-, ↑↓↑↑↓,                                                                                         |

| 3       | ↑↑↑-↑                                            |            | $\downarrow\downarrow\uparrow\uparrow\uparrow\uparrow$                                                |

|         | -^^^,                                            |            | ↑-↓, ↓-↑, -                                                                                           |

| 4       | $\downarrow\uparrow\uparrow\uparrow\uparrow$ ,   | 14         | $\uparrow\uparrow\downarrow\downarrow$ ,                                                              |

|         | • • • • • • •                                    |            | $\downarrow\uparrow\uparrow\downarrow-, -\downarrow\uparrow\uparrow\downarrow,$                       |

|         | ↑↑↑↑↓                                            |            | $\downarrow\downarrow\uparrow\uparrow\uparrow$ -                                                      |

|         | <u>↑</u> ↑↑,                                     |            | $\downarrow -\uparrow -\downarrow, \qquad \downarrow \uparrow \uparrow \downarrow \downarrow,$        |

| 5       | ↑ <b>↑</b> ↑,                                    | 15         | $\downarrow \downarrow \uparrow \uparrow \downarrow $                                                 |

| 5       | -↑↑-↑, ↑-                                        | 15         | $\downarrow \downarrow \uparrow - \downarrow,  \downarrow -$                                          |

|         |                                                  | 10         | $\downarrow \downarrow   = \downarrow, \downarrow =$                                                  |

|         | <u>↑</u> ↑-                                      | 16         | $\uparrow \downarrow \downarrow$                                                                      |

|         | <b>↑-</b> ↑-↑,                                   | 17         | ↑↓↓, ↓↓↑-                                                                                             |

| 6       | $\uparrow\uparrow\uparrow\downarrow\uparrow$ ,   | 17         | -,                                                                                                    |

|         |                                                  |            | -↓↑-↓, ↓-                                                                                             |

| _       | $\uparrow \downarrow \uparrow \uparrow \uparrow$ |            | ↑↓-                                                                                                   |

|         | -↑↑↑↓,                                           |            | ↑↓-, -↓↑, ↑-                                                                                          |

| 7       | ↓↑↑↑-                                            | 18         | $\uparrow\downarrow\downarrow$ ,                                                                      |

|         | ↑↑-, -↑↑-                                        |            | $\uparrow \downarrow \uparrow - \downarrow, \qquad \downarrow - \uparrow \downarrow \uparrow,$        |

|         | -,                                               |            | ↓↓↑-↑                                                                                                 |

| 8       | <b>↓-</b> ↑↑↑,                                   |            | ↑↓↑, ↑↓↑-                                                                                             |

|         | ↓↑↑-↑,                                           | 19         | -,                                                                                                    |

|         | <b>↑-</b> ↑↑↓,                                   |            | _↓↑-↑, ↑-                                                                                             |

|         | ↑↑↑-↓                                            |            | ↑↓-                                                                                                   |

|         | · · · · · ¥                                      |            | $\uparrow \uparrow \downarrow \uparrow$ ,                                                             |

| 9       | ↓↑↑↑↓                                            | 20         | ↑↓↑-↑                                                                                                 |

|         | - + + + + + + + + + + + + + + + + + + +          | 20         |                                                                                                       |

| 10      |                                                  | 21         | ↑                                                                                                     |

| 10      | ↓↑↑,<br>^^                                       | <i>∠</i> 1 | $\downarrow \downarrow \uparrow \downarrow \downarrow$                                                |

|         | -↑↑-↓, ↓-                                        | 22         | $\downarrow \downarrow \uparrow \downarrow -, -$                                                      |

|         | <u> </u>                                         | 22         | $\downarrow \uparrow \downarrow \downarrow$                                                           |

|         | ↓-↑↑↓,                                           |            | $\downarrow\uparrow\downarrow\uparrow\downarrow$ , $\uparrow\downarrow\uparrow\downarrow\downarrow$ , |

| 11      | ↓↑↑-↓                                            | 23         | ↓↓↑↓↑                                                                                                 |

|         | †-†, †-†-                                        |            | ↑↓↑↓-, -                                                                                              |

|         | -,                                               | 24         | ↓↑↓↑                                                                                                  |

| 12      | -↑↑↓↑,                                           |            |                                                                                                       |

|         | ↑ <b>↑</b> ↑↓-,                                  | 25         |                                                                                                       |

|         | -↓↑↑↑,                                           |            | $\uparrow \downarrow \uparrow \downarrow \uparrow$                                                    |

|         | ↑↓↑↑-                                            |            |                                                                                                       |

| L       |                                                  |            |                                                                                                       |

capacitances, driver strengths, and signal timing characteristics.

In figure (7), a new analytical five-wire delay model is proposed in which two extra neighboring wires are included in the RC interconnect model which gives better accuracy than the 3-wire RC interconnect model.

#### 3. Literature Review

The performance of interconnect drivers degrade due to reliability mechanisms such as bias temperature instability

(BTI) and hot carrier injection (HCI) depends on the length and width of an interconnect wire. The dependence of bias temperature instability (BTI) and hot carrier injection (HCI)-induced frequency degradation on interconnect length has been examined for the first time [1]. To cope with crosstalk delay accurate delay models of coupled interconnects are needed. In particular, delay models based on analytical approaches are desirable, because they are not only largely transparent to technology, but also explicitly establish the connections between delays of coupled interconnects and transition patterns, thereby enabling crosstalk alleviating techniques such as crosstalk avoidance codes. An equalized on-chip global link structure was proposed employing a tapered CML driver, CTLE, and SAbased latch. Applying SQP nonlinear optimization methods for a driver-receiver cooptimization demonstrated the lowest energy/bit for the global link performance [2]. With Fourier series and Fourier integrals, a new and systematic approach, called the Amir and Nasser (AMN) method, is proposed to derive exact analytical expressions for step input response of distributed resistance capacitance (RC), inductance-capacitance (LC), and resistance-inductance capacitance (RLC) models of interconnects [3].

Crosstalk avoidance codes (CACs) used to alleviate the crosstalk delays by restricting the transition patterns on a bus. This paper proposed more number of crosstalk classes as compared to previous crosstalk classes as the delays of its classes do not overlap, both leading to more accurate control of delays and reduced delays and

improved throughput. This crosstalk class has wider variety of tradeoff between bus delays and efficiency [4]. A realizable-II model for the driving-point impedance of an RLC current-mode transmission line is derived. The output current of an RLC current-mode transmission line is also derived. The model is extended to multiple parallel coupled interconnects with inductive and capacitive coupling between them In currentmode signaling the major difference over voltagemode is the resistive termination at the receiver end. Accurate and efficient models are needed for current-mode signaling for issues such as energy dissipation and propagation delay. In voltagemode signaling, the dynamic energy dissipation has traditionally been obtained from the wellknown equation  $E = CV_{dd}^2$ , where C is the total capacitance [5].

3-D interconnect techniques in multilayer very large scale integration design, such as stacked layers and various chip stacking systems, have paved the way for the improvement of integrated circuit density and operation speed. However, these techniques often accompany with impedance discontinuities that induce signal integrity integrity (SI)/power and electromagnetic interference effects in this paper a no conformal domain decomposition method with second-order transmission condition for SI analysis of highspeed interconnects on a multi scale multilayer printed circuit board is proposed [6]. Over the past two decades, wire widths of interconnects have reduced by two orders of magnitude and at the same time the device density on the chips has increased by more than five orders of magnitude. Consequently, the current density in signal wires has increased, thereby making them extremely vulnerable to electro-migration (EM) failures. EM is a process in which mass transport takes place because of interaction between the moving electrons and the metal ions at high current densities. Migration of metal ions results in metal build-up or depletion resulting in catastrophic disconnections in the form of hillocks and voids. An improved and efficient method for static estimation of average and root-mean-squared currents used for electro migration (EM) reliability analysis is presented in this work. Significantly different from state-of-the-art, the

proposed method gives closed-form expressions for average and RMS currents in one complete cycle. The proposed method can be readily configured to work with different combinations of ramp and exponential waveforms [7].

To minimize worst-case crosstalk patterns in bus lines by using simulated annealing (SA)-based high-level synthesis solutions for a given data environment with correlations that do not result in such worst-case patterns. Besides synthesis moves, bus re-ordering and data transfer invert encoding is incorporated [8]. Fast waveform estimation (FWE) technique is used to estimate the output waveform for general RC interconnect networks in the presence coupling noise, while the static methods suffers from inaccuracy and instability to capture the non-monotonic nature of signal waveform in the presence of coupling noise. The accuracy of FWE is comparable to the general model order reduction based methods while maintaining an efficiency that is comparable to Elmore delay based analysis. FWE approach provides an efficiency that is comparable to like asymptotic waveform evaluation (AWE) [9].

To maximize quality while minimizing costs, the automotive engineer must uncover, understand, and eliminate crosstalk problems early in the design process, Closed-form estimates of worst or nearly worst case crosstalk can be useful in system analysis, since these estimates can quickly identify problem areas that require close inspection and they show a clear relationship between design parameters and crosstalk that allows intelligent modification of the system [10].

In DSM technology due to shrink in feature size of ICs CMOS gate driven interconnect become critical issues. Signal integrity (SI) is strongly affected by both the transmission line behavior of interconnects and the nonlinear behavior of CMOS drivers. Modeling of lossy interconnects with frequency-dependent line parameters has analyzed with FDTD and quite suitable for SI analysis in high-speed interconnect systems [11]. Crosstalk delay may be several times more than the delay of bus. The crosstalk delay has become a bottleneck in deep submicrometer system on chip

designs. Crosstalk delay is reduced by skewing the timing signals on the bus, bus interleaving, precharging, or using repeaters. These solutions have varying degrees of success and are often technology dependent, power consuming or suitable to process variation. A technology independent solution to this problem is shielding which cuts the worst-case crosstalk delay by half, but it nearly doubles the wiring area [12]. Propagation delay across long on-chip buses is significant when adjacent wires are transitioning in opposite direction (i.e., crosstalk transitions) as compared to transitioning in the same direction. By employing Fibonacci, code it can be avoided [13]. A lie formula is used to convert the solution of the transmission line network into delay algebraic equations to obtain the time domain response. This algorithm can be used to model both identical and non-identical multiconductor lines and loads [14]. Crosstalk-induced latency is predicted by analyzing the possible crosstalk effects of adjacent patterns stored in an NOC router. Transition times of selected bits are then adjusted to relieve these predicted crosstalkinduced effects. It requires no extra wires comparison to shielding technique [15]. A utilitarian theory is proposed for multimetric optimization of delay, dynamic power, leakage power, and crosstalk noise, via gate sizing [16]. For fast and accurate modeling of the distributed RLC interconnect and transmission lines a closed forms of the state-space models and the recursive algorithms is used in this paper, which may be evenly or unevenly distributed. Considered models include the distributed RLC interconnect lines with or without external source and load connection. The importance is their modeling accuracy and very low computation complexity [17]. The crosstalk-induced delay, noise, and CMP-induced thickness-variation implications of dummy fill generated using rule-based wire track fill techniques and CMP-aware model-based methods for designs implemented in 65 nm process technology. The impact of fill metal is examined on several interconnect test structures, which provides important insights into the performance and reliability implications of both interlayer and interlayer capacitive coupling due to dummy fill and their effect on crosstalkinduced delay and noise and then explore the crosstalk-induced timing, noise, capacitance, and CMP-induced thickness-variation implications of on several large-scale designs fill metal implemented in 65 nm process technology [18]. With depth analysis of signal slew and skew variation, the variations of rise/fall time and skew alter the behavior of coupled inductive lines under different switching patterns [19]. A  $2\pi$  RLC interconnect model is used to investigate the effects of both coupling capacitance and mutual inductance on the crosstalk noise. Physical spacing and shield insertion are compared in terms of the coupling noise on the victim line for several technology nodes. a shield line can degrade rather than enhance signal integrity due to increased P/G noise coupling on the victim line [20]. Delaynoise strongly depends on the skew between the victim-aggressor driver input transitions, it is not possible a priori identify the victim-driver input transition that results in the worst-case delay-noise coupling capacitance accounts for more than 85% of the total interconnect capacitance [21]. Due to rapid scaling of process technologies has led to greatly improved performance at the cost of increased power consumption, most prominently leakage power. Dynamically pulsed MTCMOS with bus encoding for reduction of total power and crosstalk noise is proposed [22].

#### 4. Conclusion

Crosstalk in on chip VLSI interconnects is a major issue when the operating clock frequency is beyond GHz range. Due to crosstalk delay, reliability, and power consumption affects.

### 5. Acknowledgment

Author of this review article is a PhD Scholar I.K. Gujral Punjab Technical University (PTU) Jalandhar.

### 6. References

[1] Xiaofei, Qianying Tang,Dong Jiao, and Chris H. Kim, "The Dependence of BTI and HCI Induced Frequency Degradation on Interconnect Length and Its Circuit Level Implications," IEEE Transaction on Very Large Scale Integration (VLSI) Systems, Vol. 23, No. 2, Feb. 2015.

[2] Feng Shi, Xuebin Wu, and Zhiyuan Yan, "Improved Analytical Delay Models for RC coupled Interconnects" IEEE Transaction on Very Large Scale Integration (VLSI) Systems, Vol. 22, No. 7, pp. 1639 – 1644, July 2014.

[3] Shih-Hung Weng, Yulei Zhang, James F. Buckwalter, and Chung-Kuan Cheng, "Energy Efficiency Optimization Through Codesign of the Transmitter and Receiver in High-Speed On-Chip Interconnects" IEEE IEEE Transaction on Very Large Scale Integration (VLSI) Systems, Vol. 22, No. 4, pp. 938 – 942, April 2014.

[4] Amir Reza Baghban Behrouzian and Nasser Masoumi, "Analytical Solutions for Distributed Interconnect Models—Part I: Step Input Response of Finite and Semi-Infinite Lines" IEEE Transaction on Very Large Scale Integration (VLSI) Systems, Vol. 22, No. 12, pp. 2596 – 2606, December 2014.

[5] Feng Shi, Xuebin Wu, and Zhiyuan Yan, "New Crosstalk Avoidance Codes Based on a Novel Pattern Classification" IEEE Transaction on Very Large Scale Integration (VLSI) Systems, pp. 1-11, February 2012.

[6] Sampo Tuuna, Ethiopia Nigussie, Jouni Isoaho, and Hannu Tenhunen, "Modeling of Energy Dissipation in RLC Current-Mode Signaling" IEEE Transaction on Very Large Scale Integration (VLSI) Systems, Vol. 20, No. 6, pp. 1146-1151, June 2012.

[7] Yang Shao, Zhen Peng, and Jin-Fa Lee, "Signal Integrity Analysis of High-Speed Interconnects by Using Nonconformal Domain Decomposition Method" IEEE Transactions on Components, Packaging And Manufacturing Technology, Vol. 2, No. 1, pp. 122-130, January 2012. [8] Palkesh Jain and Ankit Jain, "Accurate Current Estimation for Interconnect Reliability Analysis" IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 20, No. 9, pp. 1634-1644, September 2012.

[9] Hariharan Sankaran and Srinivas Katkoori, "Simultaneous Scheduling, Allocation, Binding,Re-Ordering, and Encoding for Crosstalk Pattern Minimization During High–Level Synthesis" IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 19, NO. 2, pp. 217-226, February 2011.

[10] Jingye Xu and Masud H. Chowdhury, "Fast Waveform Estimation (FWE) for Timing Analysis" IEEE Transactions On Very Large Scale Integration (VLSI) Systems, Vol. 19, No. 5, pp. 846-856, May 2011.

[11] Xiaopeng Dong, Haixiao Weng, Daryl G. Beetner, and Todd H. Hubing, "Approximation of Worst Case Crosstalk at High Frequencies" IEEE Transactions On Lectromagnetic Compatibility, Vol. 53, No. 1, pp. 202-208, February 2011.

[12] Xiao-Chun Li, Jun-Fa Mao, and Madhavan Swaminathan, "Transient Analysis of CMOS-Gate-Driven *RLGC* Interconnects Based on FDTD" IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol. 30, No. 4, pp. 574-583, April 2011.

[13] Xuebin Wu and Zhiyuan Yan, "Efficient CODEC Designs for Crosstalk Avoidance Codes Based on Numeral Systems" IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 19, No. 4, pp. 548-558, April 2011.

[14] Madhu Mutyam, "Fibonacci Codes for Crosstalk Avoidance", IEEE Transactions on Very Large Scale Integration (VLSI) Systems

[15] Sourajeet Roy and Anestis Dounavis, "Efficient Delay and Crosstalk Modeling of RLC Interconnects Using Delay Algebraic Equations" IEEE Transactions On Very Large Scale Integration (VLSI) Systems, Vol. 19, No. 2, pp. 342-346, February 2011. [16] Ying Zhang, Huawei Li, Yinghua Min, and Xiaowei Li , "Selected Transition Time Adjustment for Tolerating Crosstalk Effects on Network-on-Chip Interconnects" IEEE Transactions On Very Large Scale Integration (VLSI) Systems, Vol. 19, No. 10, pp. 1787-1800, October 2011.

[17] Upavan Gupta and Nagarajan Ranganathan, "A Utilitarian Approach to Variation Aware Delay, Power, and Crosstalk Noise Optimization" IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 19, No. 9, pp. 1723-1726, September 2011.

[18] Sheng-Guo Wang and Ben Wang, "Modeling of Distributed *RLC* Interconnect and Transmission Line via Closed Forms and Recursive Algorithms" IEEE Transactions On Very Large Scale Integration (VLSI) Systems, Vol. 18, No. 1, pp. 119 – 130, January 2010.

[19] Arthur Nieuwoudt ,Jamil Kawa, and Yehia Massoud, "Crosstalk-Induced Delay, Noise, and Interconnect Planarization Implications of Fill Metal in Nanoscale Process Technology" IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 18, No. 3, pp. 378-391, March 2010.

[20] Abinash Roy, Jingye Xu, and Masud H. Chowdhury, "Analysis of the Impacts of Signal Slew and Skew on the Behavior of Coupled *RLC* Interconnects for Different Switching Patterns" IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 18, No. 2, pp. 338-342, February 2010.

[21] Selçuk Köse, Emre Salman and Eby G. Friedman , "Shielding Methodologies in the resence of Power/Ground Noise", IEEE Transactions on Very Large Scale Integration (VLSI) Systems

[22] Ravikishore Gandikota, Kaviraj Chopra, David Blaauw, and Dennis Sylvester, "Victim Alignment in Crosstalk-Aware Timing Analysis" IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol. 29, No. 2, pp. 261 – 274, February 2010.

[23] Harmander Singh, Rahul Rao, Kanak Agarwal, Dennis Sylvester, and Richard Brown, "Dynamically Pulsed MTCMOS With Bus Encoding for Reduction of Total Power and Crosstalk Noise" IEEE Transactions On Very Large Scale Integration (VLSI) Systems, Vol. 18, No. 1, pp. 166 – 170, January 2010.

[24] Semiconductor Industry Association, "The International Technology Roadmap For Semiconductors", 2009, Pp. 1-79.

[25] Jan M. Rabay , Anantha Chandrakasan, And Borivoje Nikolic, "Digital Integrated Circuits" , A Design Perspective Second Edition, pp. 134-172 & pp. 407-448.

# IJSER